引言

計(jì)算機(jī)體系結(jié)構(gòu)(Computer Architecture)是計(jì)算機(jī)系統(tǒng)的抽象模型,它定義了計(jì)算機(jī)各部件之間的交互方式、指令集和硬件實(shí)現(xiàn)等核心概念。而中央處理器(CPU)作為計(jì)算機(jī)的“大腦”,其工作原理是理解計(jì)算機(jī)系統(tǒng)如何高效執(zhí)行任務(wù)的關(guān)鍵。在現(xiàn)代信息技術(shù)中,計(jì)算機(jī)系統(tǒng)集成(Computer System Integration)則是將這些核心理論與技術(shù)應(yīng)用于實(shí)際,構(gòu)建穩(wěn)定、高效、可擴(kuò)展的軟硬件系統(tǒng)的綜合過(guò)程。本文將深入探討計(jì)算機(jī)體系結(jié)構(gòu)的基本框架、CPU的工作原理,以及它們?nèi)绾螢橛?jì)算機(jī)系統(tǒng)集成提供理論支撐和技術(shù)基礎(chǔ)。

一、計(jì)算機(jī)體系結(jié)構(gòu):系統(tǒng)設(shè)計(jì)的藍(lán)圖

計(jì)算機(jī)體系結(jié)構(gòu)主要關(guān)注于計(jì)算機(jī)系統(tǒng)的功能特性和用戶可見(jiàn)的接口,它定義了指令集、數(shù)據(jù)類型、寄存器組織、內(nèi)存尋址方式等關(guān)鍵要素。其核心目標(biāo)是設(shè)計(jì)出能夠高效執(zhí)行程序指令的硬件與軟件接口。

- 馮·諾依曼體系結(jié)構(gòu):這是現(xiàn)代計(jì)算機(jī)的基石,其核心思想包括:

- 程序和數(shù)據(jù)以二進(jìn)制形式存儲(chǔ)在存儲(chǔ)器中。

- 計(jì)算機(jī)由運(yùn)算器、控制器、存儲(chǔ)器、輸入設(shè)備和輸出設(shè)備五大部件組成。

- 指令順序執(zhí)行,由程序計(jì)數(shù)器(PC)控制。

- 哈佛體系結(jié)構(gòu):與馮·諾依曼結(jié)構(gòu)不同,它將程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器分開(kāi),允許同時(shí)訪問(wèn)指令和數(shù)據(jù),從而提高了執(zhí)行效率,廣泛應(yīng)用于嵌入式系統(tǒng)和數(shù)字信號(hào)處理器(DSP)中。

- 指令集架構(gòu)(ISA):這是硬件與軟件之間的關(guān)鍵接口,定義了CPU能夠理解和執(zhí)行的所有指令集合。常見(jiàn)的ISA包括x86(Intel/AMD)、ARM(移動(dòng)和嵌入式設(shè)備)和RISC-V(開(kāi)源架構(gòu))。ISA的選擇直接影響軟件兼容性、性能優(yōu)化和系統(tǒng)設(shè)計(jì)。

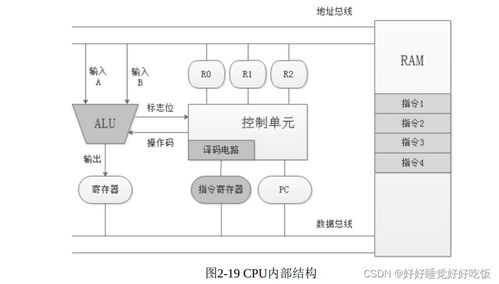

二、CPU工作原理:指令執(zhí)行的引擎

CPU是計(jì)算機(jī)體系結(jié)構(gòu)的核心執(zhí)行單元,其工作原理可以概括為“取指-譯碼-執(zhí)行”的循環(huán)過(guò)程。

- 基本組成:

- 算術(shù)邏輯單元(ALU):執(zhí)行算術(shù)和邏輯運(yùn)算。

- 控制單元(CU):協(xié)調(diào)各部件工作,解釋指令并發(fā)出控制信號(hào)。

- 寄存器組:高速存儲(chǔ)單元,用于臨時(shí)存放指令、數(shù)據(jù)和地址。

- 內(nèi)部總線:連接CPU內(nèi)部各部件的數(shù)據(jù)通路。

- 指令執(zhí)行周期:

- 取指(Fetch):從內(nèi)存中讀取下一條指令到指令寄存器(IR)。

- 譯碼(Decode):控制單元解析指令,確定需要執(zhí)行的操作。

- 執(zhí)行(Execute):ALU執(zhí)行計(jì)算或邏輯操作,可能涉及內(nèi)存訪問(wèn)或I/O操作。

- 回寫(Write-back):將執(zhí)行結(jié)果寫回寄存器或內(nèi)存。

- 性能提升技術(shù):

- 流水線(Pipelining):將指令執(zhí)行過(guò)程分為多個(gè)階段,使多條指令重疊執(zhí)行,提高吞吐率。

- 超標(biāo)量(Superscalar):在一個(gè)時(shí)鐘周期內(nèi)發(fā)射并執(zhí)行多條指令。

- 多核與多線程:通過(guò)并行處理提升多任務(wù)性能。

- 緩存(Cache):高速小容量存儲(chǔ)器,減少CPU訪問(wèn)主存的延遲。

三、計(jì)算機(jī)系統(tǒng)集成:理論與實(shí)踐的結(jié)合

計(jì)算機(jī)系統(tǒng)集成是將計(jì)算機(jī)體系結(jié)構(gòu)和CPU工作原理應(yīng)用于實(shí)際,構(gòu)建完整、可靠、高效的信息系統(tǒng)的過(guò)程。它涉及硬件選型、軟件部署、網(wǎng)絡(luò)配置和系統(tǒng)優(yōu)化等多個(gè)層面。

- 硬件集成:

- 根據(jù)應(yīng)用需求選擇合適的CPU架構(gòu)(如x86服務(wù)器、ARM邊緣設(shè)備)。

- 搭配內(nèi)存、存儲(chǔ)、主板、電源等組件,確保兼容性和性能平衡。

- 考慮散熱、功耗和物理空間等實(shí)際約束。

- 軟件與系統(tǒng)集成:

- 操作系統(tǒng)(如Windows、Linux)需與CPU架構(gòu)匹配,并優(yōu)化調(diào)度和資源管理。

- 中間件、數(shù)據(jù)庫(kù)和應(yīng)用軟件的部署需考慮CPU性能特性(如多核利用、緩存優(yōu)化)。

- 虛擬化與容器化技術(shù)(如VMware、Docker)進(jìn)一步抽象硬件,提升資源利用率。

- 網(wǎng)絡(luò)與安全集成:

- 集成網(wǎng)絡(luò)設(shè)備(交換機(jī)、路由器),確保數(shù)據(jù)高速傳輸。

- 結(jié)合CPU硬件安全特性(如Intel SGX、ARM TrustZone)構(gòu)建可信執(zhí)行環(huán)境。

- 性能調(diào)優(yōu)與監(jiān)控:

- 利用性能分析工具(如perf、VTune)監(jiān)控CPU利用率、緩存命中率等指標(biāo)。

- 根據(jù)體系結(jié)構(gòu)知識(shí)優(yōu)化代碼(如減少分支預(yù)測(cè)失誤、提高數(shù)據(jù)局部性)。

四、實(shí)際案例:從理論到應(yīng)用

以云計(jì)算數(shù)據(jù)中心為例,系統(tǒng)集成過(guò)程充分體現(xiàn)了體系結(jié)構(gòu)與CPU工作原理的重要性:

- 架構(gòu)選擇:數(shù)據(jù)中心可能混合使用x86 CPU(通用計(jì)算)和ARM CPU(能效優(yōu)化)。

- 虛擬化集成:通過(guò)CPU硬件虛擬化支持(如Intel VT-x、AMD-V),高效運(yùn)行多個(gè)虛擬機(jī)。

- 能效管理:利用CPU動(dòng)態(tài)調(diào)頻(DVFS)和電源管理技術(shù)降低能耗。

- 負(fù)載均衡:根據(jù)CPU核心利用率智能分配任務(wù),避免熱點(diǎn)。

五、未來(lái)趨勢(shì)與挑戰(zhàn)

隨著人工智能、物聯(lián)網(wǎng)和邊緣計(jì)算的興起,計(jì)算機(jī)體系結(jié)構(gòu)和CPU設(shè)計(jì)正面臨新的挑戰(zhàn):

- 異構(gòu)計(jì)算:集成CPU、GPU、FPGA等不同架構(gòu)處理器,提升特定任務(wù)效率。

- 能效優(yōu)先:在性能提升的降低功耗成為關(guān)鍵設(shè)計(jì)目標(biāo)。

- 安全性增強(qiáng):硬件級(jí)安全機(jī)制(如側(cè)信道攻擊防護(hù))日益重要。

- 系統(tǒng)集成智能化:利用AI技術(shù)自動(dòng)優(yōu)化系統(tǒng)配置和資源調(diào)度。

結(jié)論

計(jì)算機(jī)體系結(jié)構(gòu)與CPU工作原理是理解計(jì)算機(jī)系統(tǒng)如何工作的理論基礎(chǔ),而計(jì)算機(jī)系統(tǒng)集成則是將這些理論應(yīng)用于實(shí)際工程的關(guān)鍵環(huán)節(jié)。從指令執(zhí)行到系統(tǒng)部署,每一步都離不開(kāi)對(duì)硬件特性的深入理解。在技術(shù)快速發(fā)展的今天,掌握這些核心知識(shí)不僅有助于設(shè)計(jì)高效的計(jì)算機(jī)系統(tǒng),還能推動(dòng)技術(shù)創(chuàng)新,應(yīng)對(duì)未來(lái)的計(jì)算挑戰(zhàn)。對(duì)于系統(tǒng)架構(gòu)師、開(kāi)發(fā)者和集成工程師而言,持續(xù)學(xué)習(xí)體系結(jié)構(gòu)演進(jìn)和CPU新技術(shù),是構(gòu)建可靠、高性能信息系統(tǒng)的基石。